Selected Outstanding Capstone Projects in Computer Science and Information Engineering

- Published on

- Author

- 張怡婷

Selected Outstanding Capstone Projects in Computer Science and Information Engineering

With the joint efforts of our faculty and students, the capstone projects in Computer Science and Information Engineering have received wide recognition. In 2024, under the guidance of Professor Ching-Chun Huang, Wu Yi-Jing, and under the guidance of Professor I-Chen Wu, Yen-Yi Chen, both won the National Science and Technology Council’s 2024 College Student Research and Creative Works Award, showcasing the exceptional research and creative abilities of our students. This year, we are pleased to present excerpts from several outstanding capstone projects, continuing the proud tradition of excellence and inspiring more students to engage in innovative research.

Special Excellence Award

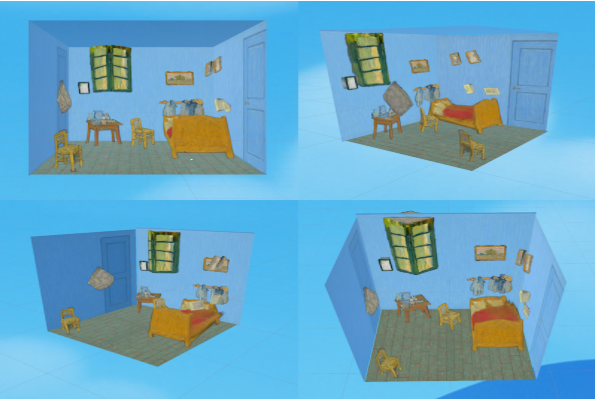

Project Title: Bringing Paintings to Life: 3D Scene Generation from Artistic Paintings

Students: Fang-Ci Tsai, Yi Chen

Advisor: Prof. Wen-Chieh Lin

Project Introduction:

This research develops an automated system capable of transforming various paintings into 3D virtual reality (VR) scenes within a short time. The system integrates multiple AI models, including semantic segmentation, depth estimation, and image inpainting, and employs Triplane Gaussian Splatting for 3D reconstruction to restore spatial depth. The scenes are then automatically imported into the Unity engine to generate explorable VR environments. Without manual modeling, a 3D VR scene can be generated within 60 minutes. Users can freely explore virtual worlds of different artistic styles, experiencing an innovative interaction that blends visual art and spatial perception. This work has broad applications in cultural preservation, game development, and art promotion.

Special Excellence Award

Project Title: Multi-Drones Automatically Pick & Place

Students: Chia-Jui Chang, Chin-Lu Chen, Hau-Chun Huang

Advisor: Prof. Yi-Ting Chen

Project Introduction:

In hazardous environments where humans cannot or should not directly enter—such as high-temperature fire scenes—autonomous drones can perform rapid reconnaissance, deliver critical supplies, and transmit information, reducing rescue risks and gaining precious response time. Our project features an automated drone system, multi-drone cooperative control techniques, and precise pick & place operations. Notably, we used indoor positioning instead of GPS to suit the application scenario. Beyond research, we participated in the Singapore Amazing Flying Machine Competition, collaborating with the HCIS Lab, NYCU Drone Club, and Maker Club, earning 4th place in Division D2. During the process, we built a simulation environment and successfully implemented simultaneous pick & place with four drones, with partial functionalities applied to real-world tests.

Excellence Award

Project Title: Gaussians Harmonizer: Recolorization for Consistent Appearance in Composite 3D Gaussian Splatting Scene

Students: Tsung-Yen Lee, Tsung-Ju Yang

Advisor: Prof. Yu-Lun Liu

Project Introduction:

We propose a solution to address visual disharmony in composite 3D Gaussian Splatting (3DGS) scenes. When objects rendered with 3DGS are directly inserted into an existing scene, noticeable inconsistencies often arise due to mismatched lighting and colors. Unlike prior approaches relying on environment maps or requiring scene-specific fine-tuning of diffusion models, we introduce an efficient and generalizable harmonization pipeline. By repeatedly applying an image harmonization network to recolor inserted foreground objects, they become visually consistent with the surrounding background. These harmonized results are then used to iteratively update the 3DGS scene. We also designed evaluation metrics for this problem. Experimental results show our method generates visually coherent composite images and outperforms existing baselines, offering a lightweight solution to improve the realism of 3D composite scenes.

Excellence Award

Project Title: Aquila-MP: A RISC-V Multi-Core SoC with Level-2 Cache Coherence

Students: Tzu-Chen Yang, Ye Chen

Advisor: Prof. Chun-Jen Tsai

Project Introduction:

This project designs and implements a multi-core SoC based on the RISC-V architecture. Building upon our lab's open-source Aquila single-core processor, we extended it into a scalable architecture supporting up to 16 cores (configurable to 2, 4, 8, or 16 cores). We incorporated a level-2 cache coherence mechanism with the MESI protocol and multi-core atomic instruction set extensions to improve parallel performance and memory consistency. The system was validated on FPGA using parallel matrix computation, OCR handwriting recognition, and parallel array sorting. Our main contribution is a lightweight and efficient snoop-based multi-core system, released as a modular open-source project. We also analyzed performance bottlenecks when scaling beyond eight cores, providing insights for future development of larger-scale multi-core systems.

Merit Award

Project Title: Window-based Rip-Up and Reroute: A Detailed Router Based on TritonRoute

Students: Tsung-Hsin Kuo, Chung Liao, Chin-Yu Fang

Advisor: Prof. Yih-Lang Li

Project Introduction:

This project enhances TritonRoute by integrating results from prior lab research. Based on a window-based framework, we proposed an adaptive rerouting strategy that manages routing within windows according to design rule check (DRC) violations. Windows are classified by violation severity, and routing is guided by the variance of wire density as a statistical indicator. By analyzing DRC and wire density performance across iterations, we identified uneven routing areas and applied more aggressive rip-up strategies to eliminate persistent violations. In challenging ISPD18 benchmark cases, our method successfully resolved violations that TritonRoute struggled with. While it slightly increased via count and wire length, CPU runtime was reduced by 38.51%, and routing robustness and design rule compliance improved, making it more applicable to real-world VLSI design flows.

Merit Award

Project Title: YearGuessr: A CLIP-Based Framework for Built-Year Prediction with Reasoning

Students: Ting-Lin Wu, Li-Zhong Szu-Tu, He Syu

Advisor: Prof. Yu-Lun Liu

Project Introduction:

The construction year of a building is vital for sustainability, cultural preservation, and safety. However, no global benchmark dataset with chronological annotations currently exists. We present YearGuessr, a dataset comprising 55,546 building façade photos from Wikipedia across 157 countries, annotated with continuous construction years (1001–2024), GPS locations, text descriptions, and view counts. We formulate year prediction as an ordinal regression problem and introduce evaluation metrics such as popularity-weighted MAE and accuracy within ±5/20/50/100 years. We benchmarked 30+ models, including CNNs, Transformers, CLIP, and vision-language models (VLMs). Our CLIP baseline, YearCLIP, shows that ordinal training halves MAE, while adding GPS information reduces errors by another 11%. Zero-shot VLMs excel on landmarks but underperform on less-known buildings, reflecting bias toward popularity. Our evaluation metrics capture this bias. The dataset is released under CC BY-SA 4.0 on Hugging Face, and code is open-sourced on GitHub. YearGuessr is the first open benchmark for millennia-scale building year prediction and reasoning.

Merit Award

Project Title: Bit-Serial RISC-V DNN Accelerator for Ultra-Low Bit-Width LLM Inference

Students: Ting-Wei Chou, Chih-Yu Chang

Advisor: Prof. Tsung-Tai Yeh

Project Introduction:

In this study, we designed a Bit-Serial RISC-V DNN accelerator to efficiently support ultra-low-bit large language model inference on edge devices. At its core is a customized processing element (PE) and instruction set integrated into the RISC-V Ara vector architecture. It natively supports asymmetric mixed-precision operations and incorporates a dynamic zero-bit skipping mechanism to eliminate redundant computations, avoiding data padding and wasted resources. Simulation results demonstrate a 16.1% reduction in execution cycles, significantly improving hardware efficiency and inference performance.